cs:sdrx02

Toto je starší verze dokumentu!

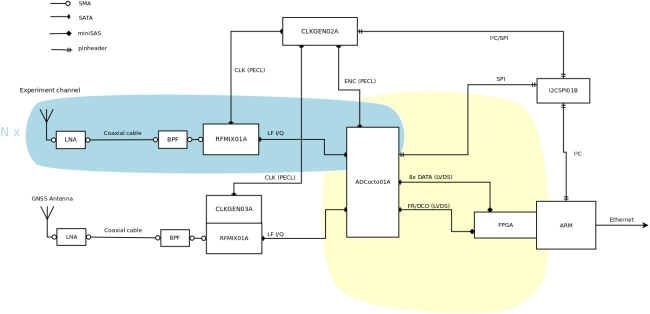

SDR přijímač SDRX02B

Na rozdíl od starší konstrukce SDR přijímače SDRX01B by nová konstrukce měla umožnit zpracovávat signály o velké šířce pásma řádově jednotek až desítek MHz ze škálovatelného počtu kanálů.

Kvadraturní směšovač

Analogově digitální převodník

Pro digitalizaci je možné využít rychlé ADC moduly adcdual, pro jednokanálový příjem, nebo adcoctospi. Tyto moduly by v konstrukci měly být vzájemně komplementární.

Výpočetní jednotka

Potřebné parametry výpočetní jednotky jsou.

- Možnost integrace s FPGA

- Vstup pro 10 differenčních LVDS párů s bitovou rychlostí 200MHz a více.

- Implementace DSP filtrů v FPGA

- Datová propustnost do paměti minimálně 40MB/s na jeden kanál resp. anténu přijímače.

- CPU jednotka na které běží Linux, pokud možno v co nejstandardnější konfiguraci

- Alespoň 1GB RAM operační pamětí (Limituje běh GNURadia)

- Alespoň 1GHz CPU a minimálně jedno jádro.

- 1Gbit Ethernet rozhraní

- Přechodné uložiště pro data - řadič pro SDkartu, SATA rozhraní.

Zatím se předpokládá využití jednodeskového počítače parallella přímo připojeného na ADC. Spojení bude opět realizováno SATA kabely připojenými přes redukční desku BTH2DIFF

cs/sdrx02.1496935185.txt.gz · Poslední úprava: 2017/06/08 15:19 (upraveno mimo DokuWiki)