Obsah

SDR přijímač SDRX02B

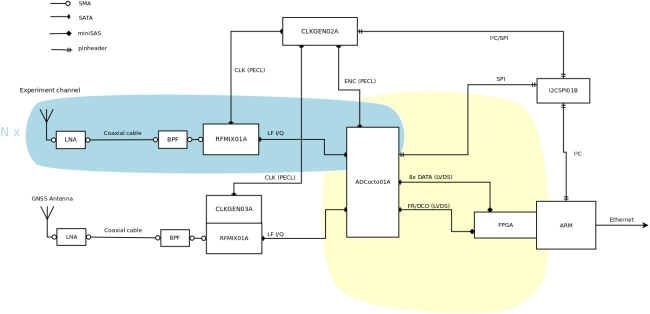

Na rozdíl od starší konstrukce SDR přijímače SDRX01B by nová konstrukce měla umožnit zpracovávat signály o velké šířce pásma řádově jednotek až desítek MHz ze škálovatelného počtu kanálů.

Blokové schéma obsahuje kromě přijímacích větví z anténního pole ještě přijímací větev referenčního GNSS signálu, který slouží k získání přesného času a frekvenčních korekcí.

Kvadraturní demodulátor

Kvadraturní demodulátor slouží k převedení vysokofrekvenčního vstupního signálu na komplexní I/Q nizkofrekvenční signál. Tento proces využívá směšování signálu se signálem z lokálního oscilátoru.

Kvadraturní směšovače vetšinou využívají architektury, které vedou na potřebu generování čtyř-fázových hodin. Kvadraturní hodiny jsou generovány interně ze signálu LO, který má dvojnásobnou frekvenci, než je reálná směšovací frekvence LO.

Integrované směšovače

Existují hotové integrované I/Q demodulátory, které zpracovávají differenční RF signál a jejich výstupem jsou differenční složky komplexního signálu.

Pro předpokládaný frekvenční rozsah vyhovuje obvod ADL5387. Který se hodí zejména pro příjem referenčního GNSS signálu.

Složené směšovací obvody

Pro některé typy antén, které mají výstupní členy s fázovým posuvem, který je potřeba správně sčítat, je výhodné použít směšovač realizovaný z diskrétních komponent. Takový směšovač pak může rovnou fázový posuv i využít. Například SC-QHA anténa má na výstupech kvadraturní signál, který je možné přímo převádět na I/Q signál dvěma standardními směšovači napájenými ze společného zdroje frekvenčního signálu.

Analogově digitální převodník

Pro digitalizaci je možné využít rychlé ADC moduly adcdual, pro jednokanálový příjem, nebo adcoctospi. Tyto moduly by v konstrukci měly být vzájemně komplementární.

Generátor hodinového signálu

Generátor hodinového signálu je potřebný k vytváření vzorkovacího kmitočtu ADC a dále pro generování signálů pro spínané směšovače. V původních konstrukcích byla tato úloha řešena použitím GPS disciplinovaného oscilátoru využívajícího standardní GPS přijímač. Toto řešení je však závislé na algoritmech zpracování signálu v použitém přijímači. Pro staniční stacionární aplikace je však vhodnější hodinový signál generovat volně běžícím oscilátorem s nízkým šumem. A pouze zaznamenávat jeho dlouhodobé frekvenční chyby. Tím je dosaženo stabilnějších parametrů oscilátoru. Je však potřeba vyřešit softwarové zpracování GNSS.

Výpočetní jednotka

Potřebné parametry výpočetní jednotky jsou.

- Možnost integrace s FPGA

- Vstup pro 10 differenčních LVDS párů s bitovou rychlostí 200MHz a více.

- Implementace DSP filtrů v FPGA

- Datová propustnost do paměti minimálně 40MB/s na jeden kanál resp. anténu přijímače.

- CPU jednotka na které běží Linux, pokud možno v co nejstandardnější konfiguraci

- Alespoň 1GB RAM operační pamětí (Limituje běh GNURadia)

- Alespoň 1GHz CPU a minimálně jedno jádro.

- 1Gbit Ethernet rozhraní

- Přechodné uložiště pro data - řadič pro SDkartu/ SATA rozhraní.

Zatím se předpokládá využití jednodeskového počítače Parallella přímo připojeného na ADC. Spojení bude realizováno differenčními signály připojenými přes redukční desku. Parallella Embedded má k dispozici 24 párů, které lze využít pro připojení až 8mi prvkového anténního pole.